# 次世代スーパーコンピュータのシステム 構成案について

平成19年4月27日

理化学研究所 次世代スーパーコンピュータ開発実施本部

#### 目次

- 1. 概念設計について

- 2. システム構成の考え方

- 3. システム構成案

- 3.1 統合汎用スーパーコンピュータシステムの概要

- 3.2 **ユニットAの概要**

- 3.3 ユニットBの概要

- 4. 要素技術について

- 5. ベンチマーク・テスト性能評価について

# 1. 概念設計について

## 概念設計の概要

- NEC + 日立チーム(NH)と富士通(F)の2者が,次世代スーパーコンピュータ・システムの概念設計を実施.

- 期間: 平成18年9月19日 平成19年2月28日

- 概念設計の主な要求仕様

- ピーク性能10PFLOPS以上,メモリ容量2.5PB以上,消費電力30MW以下(周辺機器,空調機器を含む),設置面積3,200㎡以下(周辺機器を含む)

- ただし、最終仕様ではメモリ容量や磁気ディスク容量は変動の可能性あり、

- 平成18年12月1日,2者から中間報告を受領.内容は以下の通り.

- システム構成

- システム仕様及び構成図

- システム諸元(設置面積,消費電力等)

- ソフトウェア・スタックと機能概要

- ベンチマーク・テストによる性能予測結果

- SimFold, GAMESS, Modylas, RSDFT, NICAM, LatticeQCD, LANS

- HPL, NPB-FT

- 中間報告結果を開発グループで評価.

- 最終報告書を受領(平成19年2月28日)

- 成果報告を評価

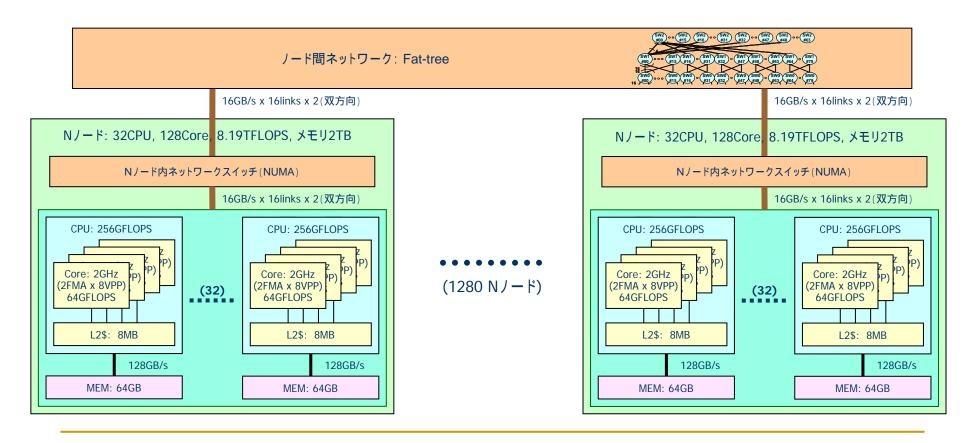

## NH案のシステム構成

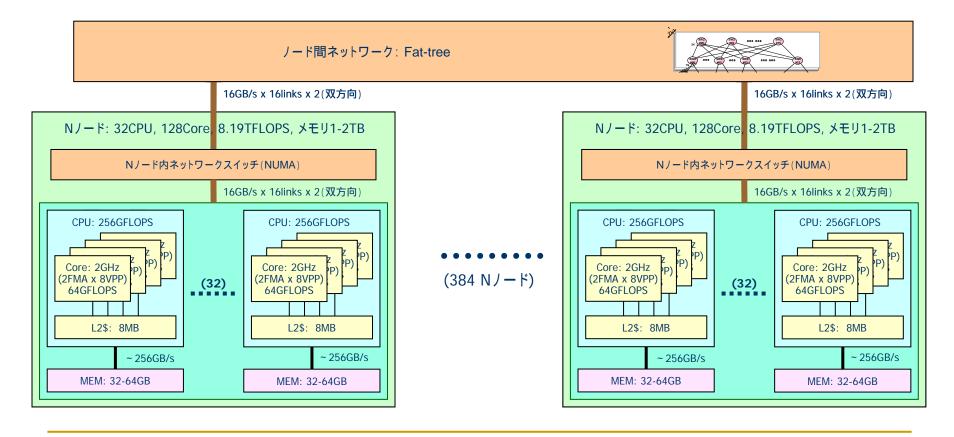

■ 計算ノード数:1,280(Nノード),40,960(SMP)

CPU数: 40,960コア数: 163,840

■ ピーク演算性能: 10.48PFLOPS

■ メモリ総容量: 2.5PB (Nノード当り2TB)

■ インターコネクトネットワーク: Fat-tree

■ 3段のFat-treeを構成

■ ポート当り16GB/s双方向の32x32スイッチを採用

■ スイッチ間は20Gbpsの光接続

■ 消費電力: 17.5MW (Linpack時,磁気ディスク除く)

## 提案システムの特徴(NH案)

#### ■ プロセッサ

- 45nmプロセスによる1CPUチップ当り256GFLOPSの高演算密度実装

- 1CPU当り4コア構成,動作周波数2GHzで駆動

- コア当り2FMAx8セットの演算器と128KBの大容量ベクトルレジスタ

- 8MBを4コアで共有し、ソフトウェアでも制御可能としたRDB (Reusable Data Buffering)機能付きL2キャッシュ

- 1CPU内の4コアは(ハードによるキャッシュコヒーレンシ保証をした)SMP構成

- 全システムを40,960CPUで構成し演算性能10.48PFLOPS,主記憶2.5PBを実現

- システム運用のために、Nノード内の32CPUが論理的にメモリ空間を共有し、一つのOSで動作(MPIプロセスはCPUまたはコア単位)

- 消費電力はCPUあたり140W(Linpack実行時)

#### ネットワーク

- バイセクションバンド幅328TB/s, 3段のFat treeで1280 Nノードを接続

- 光インターコネクトの採用

- 非同期転送,同報機能,高速バリア同期機能付きのデータ転送機能

- 入出力ポートの構成制御によるパーティショニング

# システム・ソフトウェアなど(NH案)

#### ソフトウェア

- OS: Linux(フロントエンドノード, IOノード), 専用OS(計算ノード)

- ミドルウェア: 運用管理,ジョブ管理,ソフトウェア配布,資源管理, グリッドミドルウェア(フロントエンド)

- ライブラリ: OpenMP, MPI, 科学技術計算ライブラリ

- ツール: 開発ツール, デバッグツール, チューニングツール

#### ■ プログラミングモデル

- 推奨モデル:分散メモリ並列,共有メモリ並列

- 言語: Fortran, HPF, CAF, C/C++, MPI

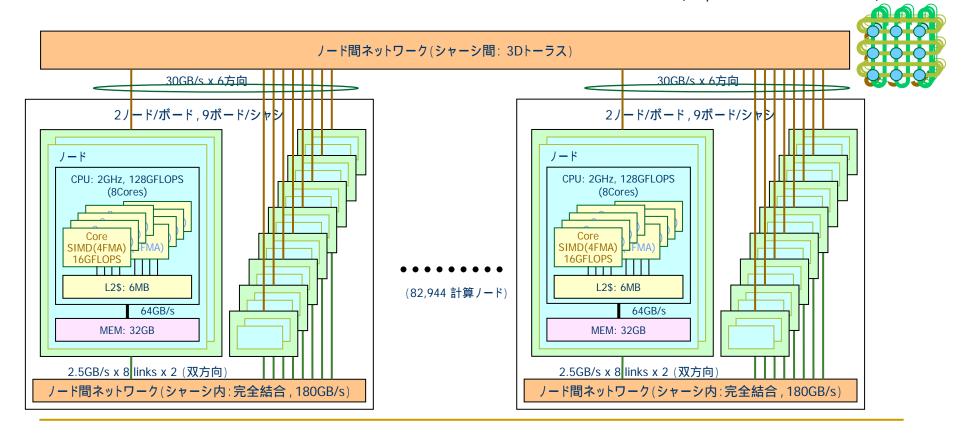

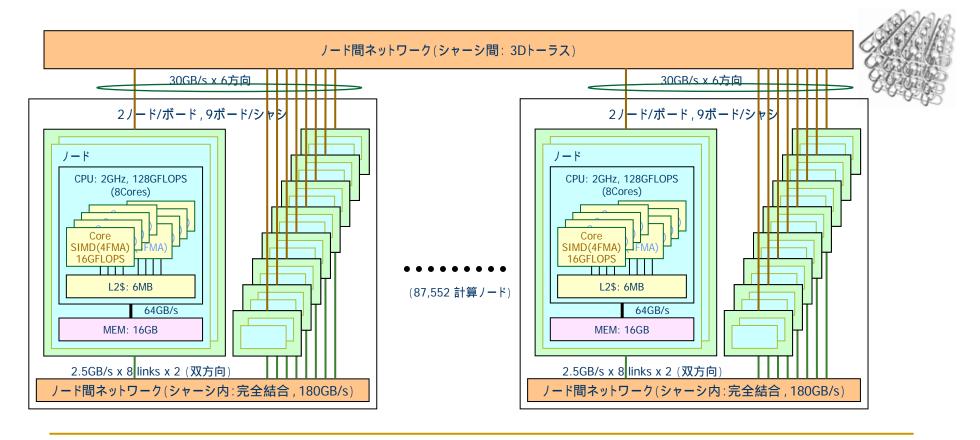

## F案のシステム構成

■ 計算ノード数: 82,944

■ CPU数: 82,944 ■ コア数: 663,552

■ ピーク演算性能:10.61PFLOPS

■ メモリ総容量2.53PB(計算ノード当り32GB)

■ インターコネクトネットワーク

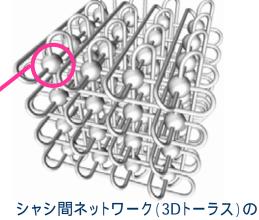

■ ToFu: 完全結合+3Dトーラス

■ 18CPUを1セットとしたシャシ内を完全結合

■ シャシ間(総数4608シャシ)を3Dトーラスで結合

● リンク当り5.0GB/s×2,1シャシから30GB/s×6方向

■ 消費電力: 15.5MW (Linpack時,磁気ディスク除く)

## 提案システムの特徴(F案)

#### ■ プロセッサ

- 45nmプロセスによる1CPU(LSI) 当り128GFLOPSの高密度実装

- 1CPU当り8コア構成,動作周波数2GHzで駆動

- コア当りFPレジスタ128本(SPARC-V9規格の4倍), SIMD拡張演算器(4FMA, 4逆数近似等)によるHPC向け拡張

- 6MBのL2キャッシュを8コアで共有,ハードバリア機構

- パリティ/剰余チェック,命令リトライによる高信頼性

- 全システムを82,944CPUで構成し,演算性能10.6PFLOPS,主記憶2.53PBを 実現

- 消費電力: Linpack時 58W/CPU (ジャンクション温度20 時)

- ネットワーク: ToFu (Torus-connected Full connection)

- 18CPUを1セットとしたシャシ内を完全結合,シャシ間を3Dトーラス結合した独自方式

- 隣接通信を重視した設計思想

- 次元毎に2シャシ単位で直方体分割することによるパーティション運用

## システム·ソフトウェアなど(F案)

#### システムソフトウェア

- OS: POSIX規格準拠のUNIX系オープンOS

- ミドルウェア:運用管理,ジョブ管理,ソフトウェア配布,資源管理, グリッドミドルウェア(フロントエンドサーバ)

- ライブラリ: OpenMP, MPI, 科学技術計算ライブラリ

- ツール: 開発ツール, デバッグツール, チューニングツール

#### ■ プログラミングモデル

- 8コアSMPの分散結合メモリ並列,または8コアSMP×完全結合× 3Dトーラス(ToFuトポロジに対するプロセス最適配置)

- 言語: Fortran, XP Fortran, HPF, CAF, C/C++, MPI

# 提案システム全体の比較

|                    | NH案                     | F案                        |

|--------------------|-------------------------|---------------------------|

| ピーク演算性能(PFLOPS)    | 10.48                   | 10.61                     |

| 総メモリ容量(PB)         | 2.50                    | 2.53                      |

| 総ディスク容量(PB)        | 140                     | 140                       |

| 設置面積:計算装置部/全体(m²)  | 1,446 / 2,976           | 1,475 / 3,198             |

| 消費電力:計算装置部/全体(MW)  | 17.5 / 23<br>(Linpack時) | 15.5 / 22.8<br>(Linpack時) |

| 総計算ノード数(= CPUチップ数) | 40,960                  | 82,944                    |

| 総演算コア数             | 163,840                 | 663,552                   |

| 計算ノード間ネットワーク       | Fat Tree                | 複合(完全結合 +<br>3Dトーラス)      |

# 提案システムの演算部性能の比較

|                       |                        |           | NH案                        | F案              |

|-----------------------|------------------------|-----------|----------------------------|-----------------|

| 演算コア                  | 動作周波数(GHz)             |           | 2                          |                 |

|                       | 演算性能(GFLOPS)           |           | 64                         | 16              |

|                       | 演算加速機構 (演算器数)          |           | ベクトル型<br>(16: 2FMA x 8VPP) | SIMD型<br>(4FMA) |

|                       | レジスタファイル               |           | ベクトルレジスタ<br>256要素×64本      | スカラレジスタ<br>128本 |

| CPUチップ<br>(計算<br>ノード) | 演算性能(GFLOPS)           |           | 256                        | 128             |

|                       | 演算コア数                  |           | 4                          | 8               |

|                       | メモリバンド幅<br>(Byte/Flop) |           | 0.5                        |                 |

|                       | L2<br>キャッシュ            | 容量(MB)    | 8                          | 6               |

|                       |                        | Byte/Flop | 4                          | 2               |

|                       |                        | 特殊機構      | 選択的登録機構                    | ライン・ロック機構       |

## 提案システムに対する考察(その1)

- 両者共通の設計思想: 高性能・低電力システムを追求

- 電力対性能を重視した並列アーキテクチャ

- 動作周波数 (2GHz) を押さえて電力低減

- マルチコア: 半導体高集積技術の活用

- Thin / ード: Fat / ードに比べ電力対性能比で優位

- 超並列: NH案 40,960ノード, F案 82,944ノード

- 演算加速機構(演算器数増強)とレジスタファイル

- コアあたりの演算器数増強による効率よい高速演算

- 多数演算器に見合ったレジスタファイル装備

- HPC指向のオンチップ・メモリ・アーキテクチャ

- キャッシュ,ローカルメモリ混在アーキテクチャ

## 提案システムに対する考察(その2)

- 電力対性能比,及び面積対性能比はほぼ同等

- 計算ノードの並列度は大差なし(2:1)

NH案 : 約4万計算ノード(演算コア: 約16万)

F案 : 約8万計算ノード(演算コア: 約66万)

- 設計思想の違い

- 演算加速機構

NH案 :ベクトル型 演算器拡張性重視

F案:SIMD型: 汎用性,柔軟性重視

■ 計算ノード間ネットワーク

NH案 : Fat Tree 汎用性重視

F案 : 3Dトーラス 次々世代を見据えた拡張性重視

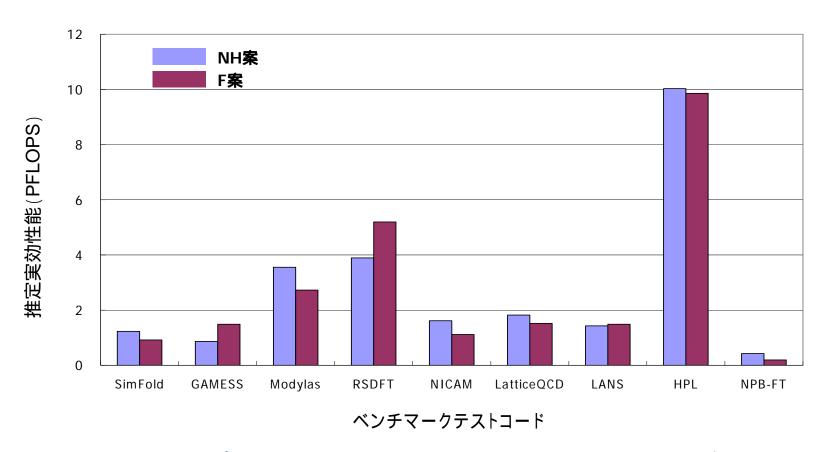

## ベンチマーク・テストによる性能評価について

- ベンチマーク・テスト・プログラム(21本)の実行時間を推定

- 特に,ベンチマーク・テスト・プログラム(9本)について,詳細に評価

- ターゲット・アプリケーションから7本のベンチマーク・テスト

- SimFold , GAMESS , Modylas , RSDFT , NICAM , LatticeQCD , LANS

- HPL(High Performance Linpack), NPB-FT

- 推定方法は,両者独自の手法を採用

- 実機での計測値から推定

- 新たなアーキテクチャ部分は,机上で分析,評価

#### ベンチマーク・テストによる性能予測(詳細9本)

- ターゲット・アプリケーションから7本のベンチマーク・テスト,及びHPL, NPB-FTについて,実効性能を推定.

- いずれのベンチマーク・テストもほぼ同等の性能.

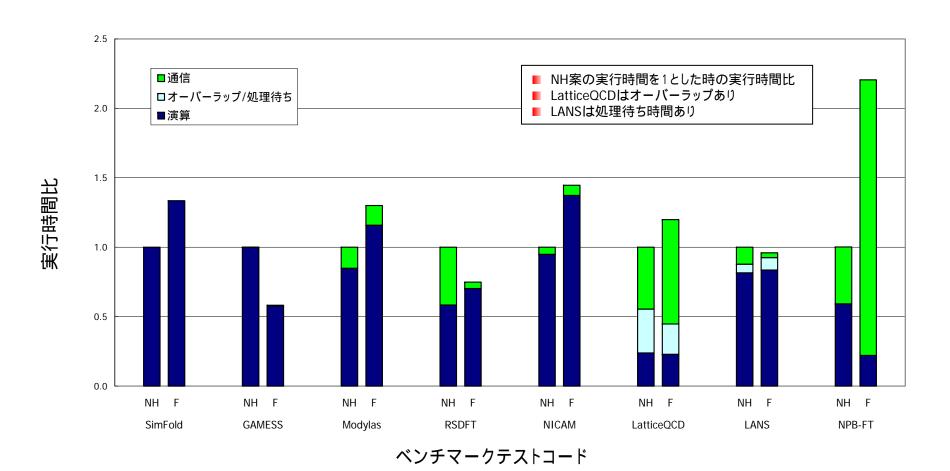

#### ベンチマークテストによる性能予測(実行時間比:詳細9本)

RSDFT及びNPB-FTは,通信時間の差が大きい.

ネットワーク・トポロジの違いが影響している。

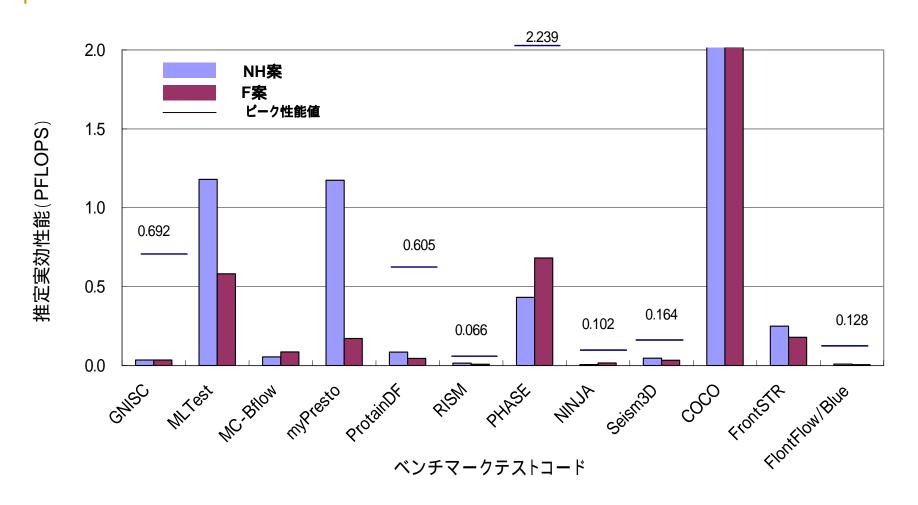

#### ベンチマーク・テストによる性能予測(他12本)

- 各BMTの最大並列数からピーク性能を設定し、その範囲内で性能予測を実施.

- チューニング等に差がある。

## 概念設計中間報告の評価結果

#### ■ 両提案に対する評価

- 概念設計の要求仕様(ピーク性能10PFLOPS以上,メモリ容量2.5PB以上,消費電力30MW以下,設置面積3,200㎡以下など)を満足.

- ベンチマーク・テスト(BMT)による性能推定結果,電力性能比等はほぼ同等.

#### ■ CPUに対する評価

- F案は,既存スカラプロセッサと親和性が高く,より幅広い技術展開が 可能.

- NH案は,ベクトルプロセッサの課題を解決し,高い演算性能を容易に 達成.

#### ネットワークに対する評価

■ F案の新規性・将来性は評価できるが, 汎用性, 運用性, 実績などに優れたNH案を採用すべき.

## システム構成案検討の考え方

- 概念設計の評価結果を踏まえ,以下の2つのケースを検討.

- 2者のいずれかを選択(2者択一).

- 2者の案をベースに共同開発.少な〈とも以下の項目を満たすことが 条件.

- 共同開発のシステム構成の方が単独開発のシステムより,性能が上がること。

- 共同開発により、将来の我が国のスパコン開発の技術力、国際競争力、 ビジネス展開力等の向上に一層貢献すること。

- 開発予算の範囲内で,共同開発システムが構築できること.

- 2者のシステム構成により,目標性能達成の見込みが確認できたため,アクセラレータの採用は考慮しない。

## 2. システム構成の考え方

#### 共同開発のシステム構成の考え方

- 1. メーカから提案のあった両者の優れた技術の特長を最大限活かし,目標性能であるLINPACKの実効性能10PFLOPSを達成しつつ,様々なアプリケーションを効率よく実行し,多くのユーザのニーズに応える最適なシステムを構築する.

- 2. スカラプロセッサベースのユニットは,理論性能10PFLOPS超とする.

- ナノ・デバイスの高精細度シミュレーション等を実行するためには、 10PFLOPS超の理論性能が必要.(実効性能 約3-5PFLOPS)

- 多〈のユーザが利用可能なPCクラスタや並列サーバによる開発・実行環境 からの連続性、プログラムの移植性を重視。

- 3. ベクトルプロセッサベースのユニットは,理論性能3PFLOPS超とする.

- 雲解像大気大循環モデルによる気候変動予測等には,理論性能3PFLOPS 超が必要 (実効性能 約1PFLOPS)

- 地球シミュレータなどベクトルプロセッサ向けのプログラム資産の有効利用 を図る.

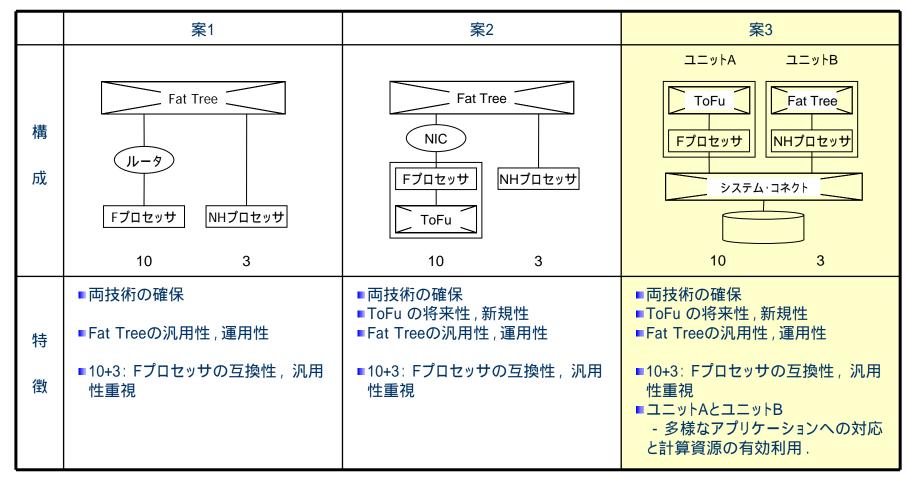

#### 共同開発システムの構成案比較

- F案プロセッサで10PFLOPS超,NH案プロセッサで3PFLOPS超の統合汎用システム 3案を検討.

- 案1,案2は開発期間の延長(約1年半)など技術的なリスクが大きい.

- 案3がベストな選択.

#### 結論

F及びNH両者の提案は,それぞれに優れた特長を持ち,一方のみを選択することは,スパコン技術の将来の可能性とリスクを考慮すると適切とは言えず,共同開発の条件を満たし,かつ技術的な実現見通しがついたことから,両者の技術を開発して,一つのシステムを構成することが最善と判断.

- ■演算加速機構を付加すること等により高性能化したスカラプロセッサ及び拡張性の高い新規のネットワーク構成によるスカラユニット(理論性能約10PFLOPS超)と、画期的な構成により高い演算性能を達成するベクトルプロセッサ及び汎用性・運用性の高い省電力ネットワーク構成によるベクトルユニット(理論性能約3PFLOPS超)の両者をシステムコネクトで結合した統合汎用システムを開発する。

- これにより、少なくとも目標性能であるLinpackの実行性能 10PFLOPSを達成する.

統合汎用スーパーコンピュータシステムユニットAコニットBFat TreeNHプロセッサシステム・コネクト共有ファイル

#### 本システム構成の特長(1/3)

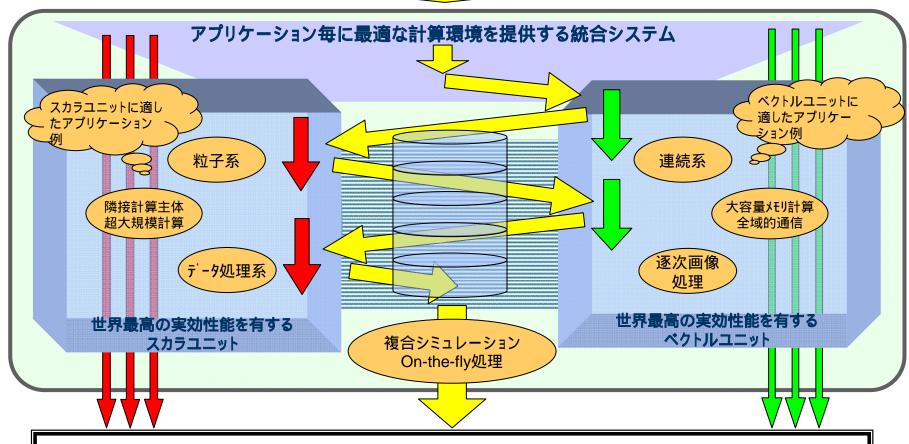

■効率的なシミュレーションの実行及びシステムの運用が可能.

両者のCPUを用いた統合汎用システムにより、ソフトウェア資産のより有効な利用や共用施設として効率的なユーザー対応ができるだけでなく、多くのアプリケーションで有効な複合シミュレーションのための最適なシステム環境を構築できる.

スカラプロセッサ向けに開発された多〈のアプリケーションと地球シミュレータに 代表されるベクトルプロセッサ向けに最適化されたアプリケーションの両方を容 易かつ発展的に利活用でき,ソフトウェア資産のより多様な有効活用が可能と なる.

多様なアプリケーションをそのアプリケーションに適したプロセッサで実行することにより,単独プロセッサによるシステムよりも計算資源を有効活用できる.

計算科学の多くのアプリケーションで見られる複合シミュレーションにおいて,最適な統合システム環境(スカラ+ベクトル)の構築が可能となる.

#### 本システム構成の特長(2/3)

■将来の我が国のスパコン開発の技術力,国際競争力等の向上に一層貢献する.

世界的主流となっているスカラプロセッサに演算加速機構を付加したプロセッサと,我が国が強みを持つベクトルプロセッサの改良型となる新しい汎用プロセッサを同時に開発することにより,次世代以降のプロセッサの技術オプションを発展させ,将来に向け国際競争力の一層の向上を図る(=次々世代の開発に繋げるために必要).

世界的に大多数のスパコンシステムが採用しているスカラプロセッサにSIMD型演算加速機構を付加すること等によりさらに高性能化を図り、将来に向け国際競争力を高めることは極めて重要・

制御構造が単純なベクトルプロセッサは、スカラプロセッサに比べ演算性能を向上させることがより容易であり、将来に向け更に高度化を図り技術を発展させることにより、我が国の重要な基幹技術の一つとなり得る.

FとNH両者の競争関係が維持され、国際的により強い技術を開発できる可能性が高まるとともに、次々世代以降のCPU開発においては、両者の技術を融合させることも視野に入れることが可能。

#### 本システム構成の特長(3/3)

■本プロジェクトの波及効果を最大化できる.

大学等の計算センターの多様なニーズを踏まえ,必要とされるスパコンの規模 やアプリケーションに対応したより柔軟な下方展開が期待される.また,メーカー の競争関係も維持される.

CPU技術及びネットワーク技術の様々な要素技術が、家電や電子機器、ビジネスサーバー等へ幅広〈展開されることが期待される。

## 3. システム構成案

#### システム構成案

- 性能目標

- ユニットA + ユニットBでLINPACK 10PFLOPS超を 達成する.

ユニットAの理論性能: 10PFLOPS超ユニットBの理論性能: 3PFLOPS超

#### 【試算】

- ユニットA: 11.2PFLOPS(ピーク性能)x 85%(LINPACK効率)=9.52PFLOPS

- ユニットB: 3.1PFLOPS(ピーク性能)x 90%(LINPACK効率)=2.79PFLOPS

# ユニットA ユニットB ToFu Fat Tree Fプロセッサ NHプロセッサ ファイル 約15PB システム・コネクト 共有ファイル 約80PB

統合汎用スーパーコンピュータシステム

ユニットA+BのLINPACK性能

90%の場合: 11.08PFLOPS 85%の場合: 10.46PFLOPS 80%の場合: 9.85PFLOPS

- 統合システム

- 統合システム機能:

- 統合スケジューラ,統合ポータルなど

- 統合共有クラスタファイルシステムなど

- システム・コネクト: 総バンド幅 約1.2TB/秒

- ▶ メモリ容量,及びファイル容量の目標仕様

- ユニットAのメモリ容量は,理論性能当たり1/8 (B/FLOPS)

- ユニットBのメモリ容量は、理論性能当たり1/4 1/8 (B/FLOPS)

- ファイルシステムの容量は,全体で約100PBとする.

- ユニットA,及びBのローカルファイルシステムの容量は、メモリ容量の10倍とする。

- 残りを共有ファイルシステムの容量とする。

- ユニットAとBの機能及び性能上の特徴を活かし,詳細設計においてさらに最適化を行う. (例:ユニットBのメモリバンド幅の強化)

- 詳細設計終了後,製造に入る前に最終構成を決定する.

#### 次世代統合汎用スーパーコンピュータシステム

多様なユーザ,多様なアプリケーション

複雑系シミュレーション、計算資源の有効利用、ソフトウェア資産の活用

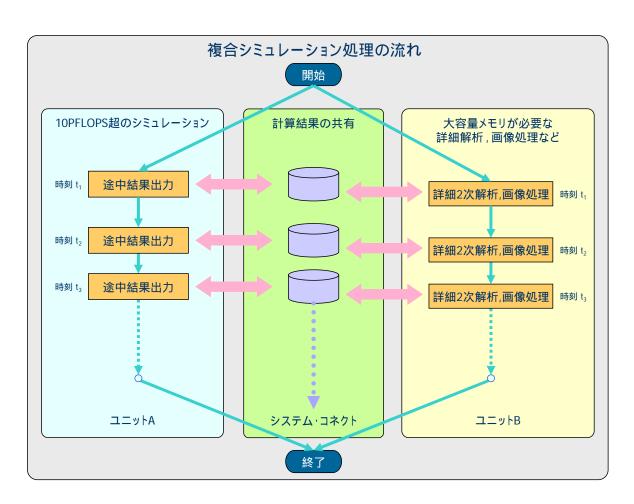

#### On-the-fly複合シミュレーション

- 統合システムによる複合シミュレーションにおいて,ある時刻ごとに出力される途中 結果の流れ作業的なデータ解析,及び画像処理に最適なシステム。

- 各ユニットとシステム・コネクトの連携により、一連のデータ処理の短縮化が可能。

- 大規模かつ長時間シ ミュレーションの途中結 果のモニタリングによる 計算資源の有効活用が 可能.

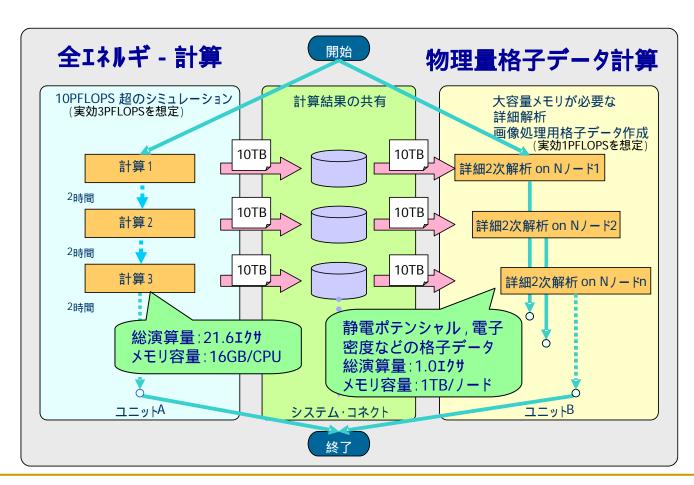

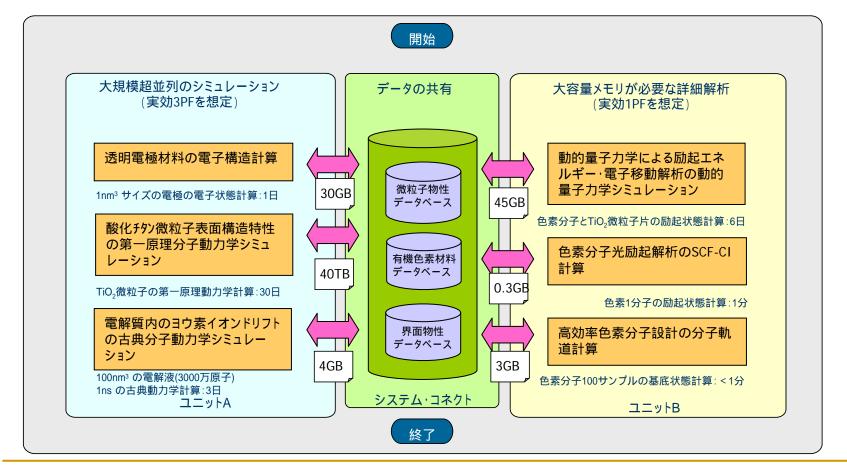

## On-the-fly複合シミュレーションの例(分子軌道計算)

- タンパク質を含む10万原子系の分子軌道計算をユニットAで実施.

- ユニットAを使い2時間程で,10TBの計算結果を出力.

- ユニットBで,各データのCG解析用格子データを作成.

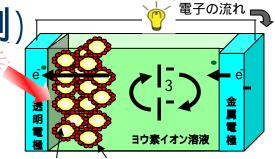

複合シミュレーション(太陽電池設計の例)

- 色素増感型太陽電池の構成要素のシミュレーション

- 構成要素毎に異なるシミュレーション技術が必要

- ユニットAとユニットBの複合計算でデバイス設計が可能

酸化チタン微粒子 有機色素分子

#### 多様なアプリケーションへの対応

- ユニットAの機能

- 理論性能で10PFLOPS超を必要とする超大規模シミュレーション (例:タンパク質解析,創薬シミュレーションなど)

- スカラ主体の既存ソフトウェアの実行

- 将来に向けた隣接通信主体のアプリケーション開発と実行

- パラメータ・スイープなどデータ処理中 心のアプリケーション実行

ユニットA ユニットB

ToFu Fat Tree

Fプロセッサ NHプロセッサ

ローカル

ファイル

約15PB

システム・コネクト

共有ファイル

約80PB

統合汎用スーパーコンピュータシステム

- ユニットBの機能

- ★容量メモリ<sup>(注)</sup>を必要とする実効性能1PFLOPSクラスの計算(例:気象シミュレーションなど)

- ベクトル計算主体の既存ソフトウェアの実行 (例:地球シミュレータ上のアプリの資産継承)

- 全対全通信主体のアプリケーションの実行(例:材料シミュレーションなど)

- 連続系シミュレーションのようなメモリ・インテンシブなアプリケーションの実行

(注) 最大1TBまでの共有メモリ(NUMA)を利用 可能.

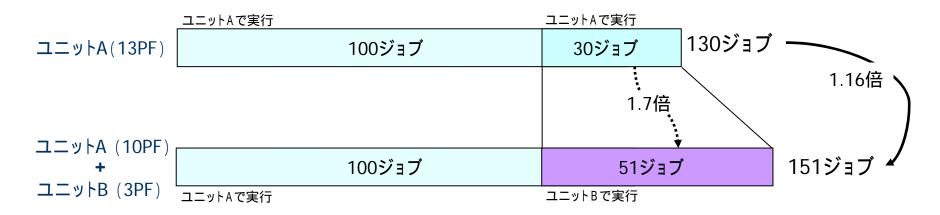

#### 計算資源の有効利用(=多数のユーザへの効率的対応)

ユニットA(13PF超)とユニットA(10PF超)+B(3PF超)とのスループット比較

ユニットA(1PF分)で一定時間内に処理する平均ジョブ数を10と仮定した場合

年間5,000人日の利用を想定しても,年間約800人日の利用拡大に繋がる.

(地球シミュレータの実績は4,500人日)

: ユニットB上で実行したほうが有効なアプリケーションのベンチマークテスト結果(計算速度比) (例) ユニットA: ユニットB NICAM(環境) 1 : 1.9 LANS(流体) 1 : 1.5

#### 3.1 統合汎用スーパーコンピュータシステムの概要

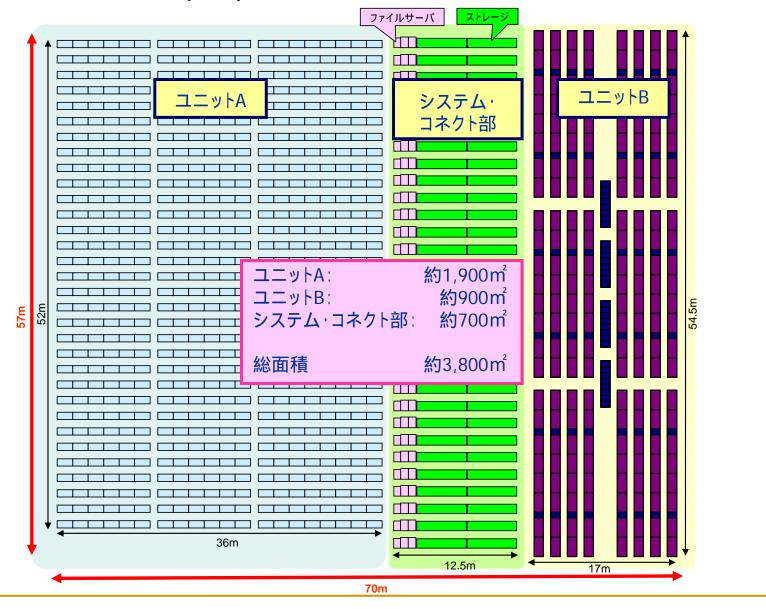

## 統合汎用スーパーコンピュータシステムの構成

■ ノード数(CPU数): 99,840

■ コア数: 749,568

ピーク性能: 14.3PFLOPS

■ メモリ容量: 1.7-2.1PB

■ 磁気ディスク容量: 約100PB

■ 消費電力: 約24MW(空調を除く) ■ 設置面積: 約3,800㎡(空調を除く)

■ 電力性能比: 約1.68MW/PFLOPS

■ 面積性能比: 約266㎡/PFLOPS

#### ユニットA

計算ノード数(CPU数): 87,552

コア数: 700,416

ピーク性能: 11.2PFLOPS

メモリ容量: 1.34PB

消費電力: 約15.2MW 設置面積: 約1,900㎡

#### ユニットB

計算ノード数(CPU数): 12,288

コア数: 49,152

ピーク性能: 3.14PFLOPS メモリ容量: 0.375-0.75PB

消費電力: 約6.8MW 設置面積: 約900㎡

ローカル ファイル 約5PB

#### システム・コネクト

- 統合システム機能

- 統合ポータル

ローカル

ファイル

約15PB

- 統合コンソール

- 統合スケジューラ

共有ファイル 約80PB システム・コネクト

総バンド幅: 約1.2TB/s 消費電力: 約2.0MW 設置面積: 約700㎡

# 統合システムとしての機能

#### 統合フロントエンド部

統合スケジューラ 統合コンソール 統合ポータル(ワークフロー,システムモニタ)

ユーザ管理(アカウント管理・課金管理)

共有クラスタファイルシステム 統合MPIライブラリ

ユニットA

共有クラスタファイルシステム 統合MPIライブラリ

ユニットB

## 統合運用システムソフトウェアの機能

- 統合フロントエンド部

- 統合スケジューラ

- メタスケジューラ機能

- 各ユニットのローカルスケジューラの統合

- ファイルのステージング連動

- 資源予約機能

- ユニットAとユニットBの資源を 同時予約し連携ジョブを実行

- 統合コンソール

- ソフトウェア構成管理

- パーティション管理

- 運用モード設定管理

- チェックポイント取得&マイグレーション

- 統合ポータル

- ワークフロー

- ユニット間連携計算自動スケ ジューリング

- ファイルのステージング支援

- システムモニタ

- ◎ ジョブ状況表示

- 統合フロントエンド部(続き)

- 統合プログラム開発環境

- クロスコンパイラ

- デバッグツール

- チューニングツール

- 共通機能

- ユーザ管理

- アカウント管理

- 課金管理

- ACL機能

- 各ユニット

- ローカル・スケジューラ

- 共有クラスタファイルシステム

- 統合MPIライブラリ

- 共通API仕様

- ユニット間高速通信インターフェース

# フロアレイアウト(例)

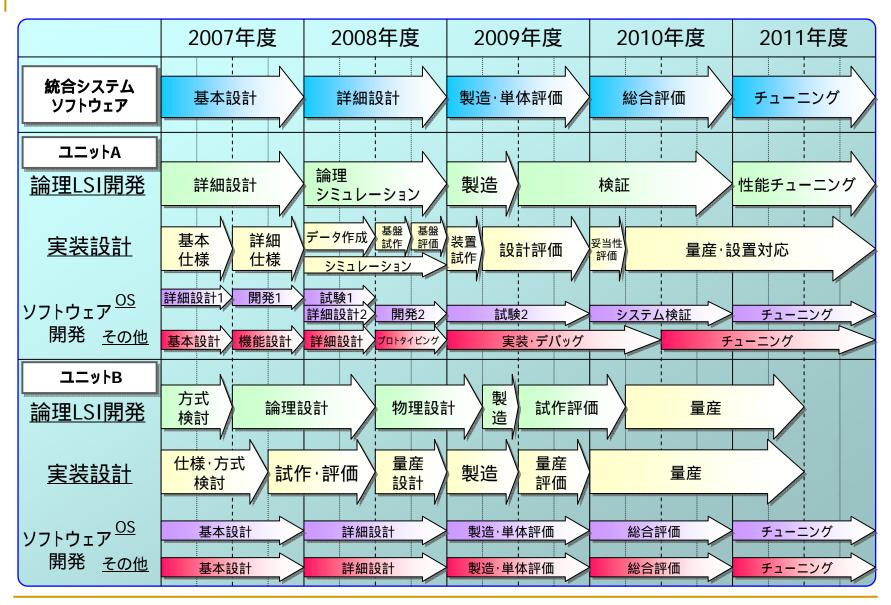

## 開発スケジュール

# 3.2 ユニットAの概要

#### ユニットAの構成図

■ 計算ノード数: 87,552

CPU数: 87,552コア数: 700,416

■ ピーク演算性能:11.2PFLOPS

■ メモリ総容量: 1.34PB(計算ノード当り16GB)

■ ネットワーク: ToFuインターコネクト(完全結合+3Dトーラス)

■ 18CPUを1セットとしたシャシ内を完全結合

■ 20x16x16(=5,120)シャシを3Dトーラスで結合

■ 消費電力: 15.2 MW (Linpack時推定,磁気ディスク除く)

#### ユニットAの特徴

#### ■ プロセッサ

- 45nmプロセスによる1CPU(LSI)当り128GFLOPSの高密度実装

- 1CPU当り8コア構成,動作周波数2GHzで駆動

- コア当りFPレジスタ128本(SPARC-V9規格の4倍), SIMD拡張演算器(4FMA, 4逆数近似等)によるHPC向け拡張

- 6MBのL2キャッシュを8コアで共有,ハードバリア機構

- パリティ/剰余チェック,命令リトライによる高信頼性

- 消費電力: 42W/CPU (Linpack時 58W/CPU, ジャンクション温度20 )

- ネットワーク: ToFu (Torus-Full connection)

- 18CPUを1セットとしたシャシ内を完全結合,シャシ間を3次元トーラス結合した 独自方式。

- 隣接通信を重視した設計思想

- 次元毎に2シャシ単位で直方体分割することによるパーティション運用

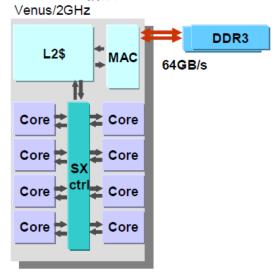

## プロセッサ構成

- 8コア構成,各コア128本のFPレジスタ を備えたスーパースカラ方式

- 動作周波数2GHz

- SIMD拡張(積和演算4個,逆数近似演 算4個など)

- コア当り16GFLOPS, CPU当り 128GFLOPS

- 大容量コア共有キャッシュ(6MB)

- ハードウェアバリア機構,ソフトウェア制御機構を装備

- 主メモリ間バンド幅は64GB/s

- 各コアとのバンド幅はロード32GB/s,ストア32GB/s

- データ供給能力は,L2キャッシュから各コアのL1キャッシュまで2B/FLOP,主メモリからL2キャッシュまで0.5B/FLOP

#### Venus構成

|                          | 仕 様                                                                           |

|--------------------------|-------------------------------------------------------------------------------|

| CPU性能                    | 128GF(16GFx8コア)                                                               |

| 動作周波数                    | 2GHz                                                                          |

| コア数                      | 8個                                                                            |

| 浮動小数点演<br>算器構成<br>(コア当り) | 積和演算器:2×2個(SIMD)拡張<br>逆数近似演算器:2×2個(SIMD)拡張<br>除算器:2個<br>比較器:2個<br>ビジュアル演算器:1個 |

| キャッシュ構成                  | 1次命令キャッシュ∶8KB(2way)<br>1次データキャッシュ∶16KB(2way)<br>2次キャッシュ∶6MB(12way)コア間共有       |

| メモリバンド幅                  | 64GB/s                                                                        |

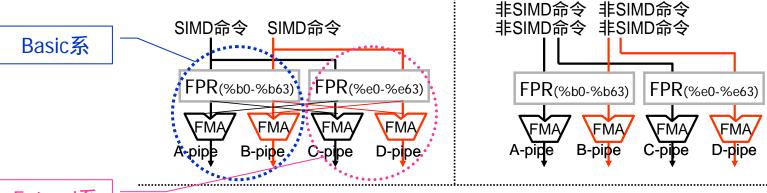

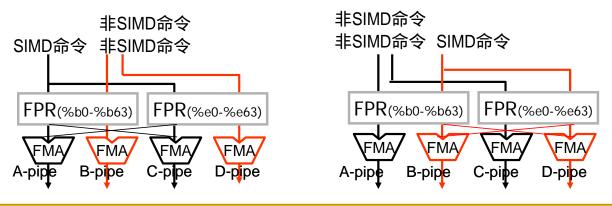

#### SIMD演算器構成

- 4命令同時発行,8命令同時ディスパッチのダイナミックスケジューリング によるアウトオブオーダ実行機能を備えたスーパースカラ

- (1) SIMD命令, 2命令を同時実行

- (2) 非SIMD命令, 4命令を同時実行

Extend系

(3) SIMD命令1命令と, 非SIMD命令2命令を同時実行

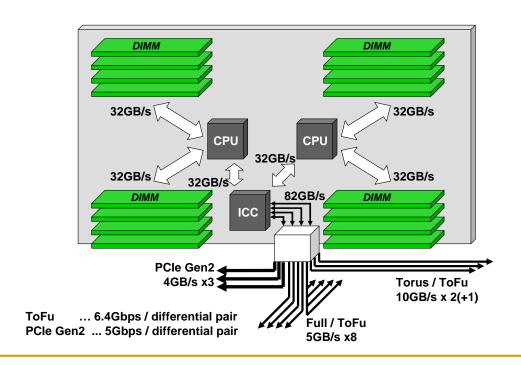

# 計算ノードとシステムボード実装

- 計算ノードは、1CPUと16GBメモリから構成。

- システムボード(SB)上に, CPU 2個,メモリ 32GB, ICC(Interconnect Controller)を搭載.

- CPU-ICC間は,32GB/sのバンド幅

- ICCは,シャシ内ネットワーク,シャシ間ネットワーク, PCI Express gen2のインターフェイスを有する.

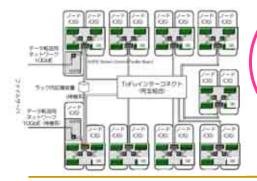

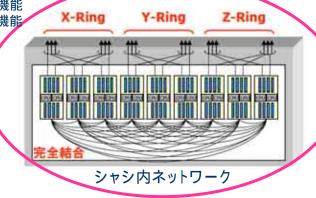

## ネットワーク構成(ToFu)

- ToFu(Torus-connected Full-connection)インターコネクト

- シャシ内ネットワークとシャシ間ネットワークの2階層ネットワーク

- シャシ内ネットワーク

- 9システムボード(SB) は完全結合

- 各接続のバンド幅

- 2.5GB/s x 2(双方向)

- ToFuの機能

- 同報通信

- 高速バリア同期機能

- 送信パケット組み立て機能

- リダクション演算支援(検討中)

- 2シャシ単位のパーティショニング

- 障害回避

- 障害リンク回避ルーティング機能

- **障害ノード回避ルーティング機能**

- シャシ間ネットワーク

- 20x16x16の3次元トーラス構成

- シャシ間バンド幅

- ◆ 5GB/s x 3リンク x 2(双方向)= 30GB/s

- ルーティング・レイテンシ

- 最小0.1 µ 秒,最大1.6 µ 秒,平均0.8 µ 秒

- MPIレイテンシ

- 最小1.1 μ 秒 , 最大2.6 μ 秒 , 平均1.8 μ 秒

イメージ

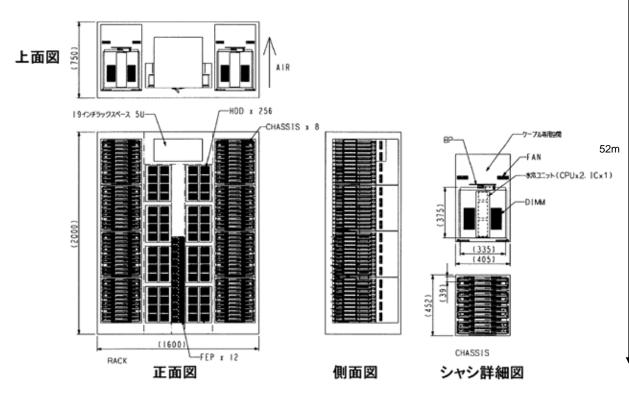

## 計算ノード筐体実装とフロアプラン

- 計算ノード筐体

- 8シャシとローカルディスクを設置

- $1600 \times 750 \times 2000 \text{ (mm}^3\text{)}$

#### ノード接続図

#### システム・ソフトウェアなど

- システムソフトウェア

- OS: POSIX規格に準じたUNIX系オープンOS

- ミドルウェア:運用管理,ジョブ管理,SW配布,資源管理,グリッドミドルウェア(フロントエンドサーバ)

- ライブラリ: OpenMP, MPI, 科学技術計算ライブラリ

- ツール: 開発ツール, デバッグツール, チューニングツール

- プログラム言語コンパイラ

- Fortran , HPF , CAF , XP Fortran , C/C++

- プログラミングモデル

- モデルA:8コアSMPの大規模並列(最大87,552)

- モデルB: ToFuネットワークをトーラスに仮想化

- ◎ トーラスを意識したプログラミング

#### RAS機能

#### CPU

- キャッシュ部でのECC機能,内蔵RAM全体での徹底したパリティチェックと自動修正機能によりデーター貫性を確保

- 演算部ではパリティチェック,あるいは剰余チェックによるデータ保護,さらに 命令リトライ機能により実行結果を保証

- これら高信頼設計と低温動作を組み合わせることでメインフレームを上回る 信頼性を達成

- 計算ノード間ネットワーク

- 障害リンク,及び障害ノードの検出と回避ルートへの自動切り替え機能

- 障害発生時にも仮想的な3次元トーラスのユーザビューを維持

- ストレージ・ファイルシステム

- ディスク,及び計算ノードからのパスの二重化によるフェイルオーバ

- 運用ソフトウェア

- 計算ノード,ファイルシステム,フロントエンド及びシステム制御サーバの的確な連携とシステム全体の信頼性の確保

# 3.3 ユニットBの概要

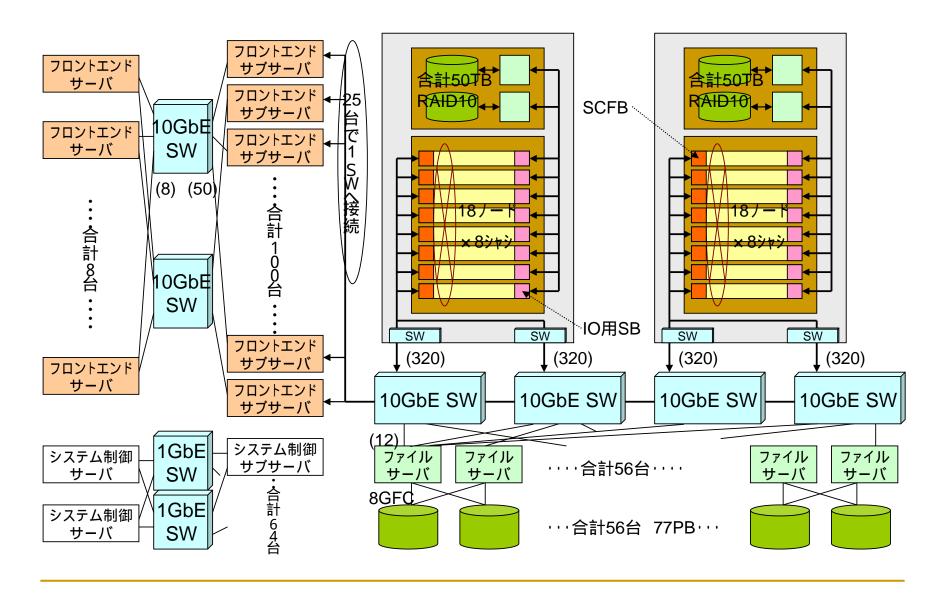

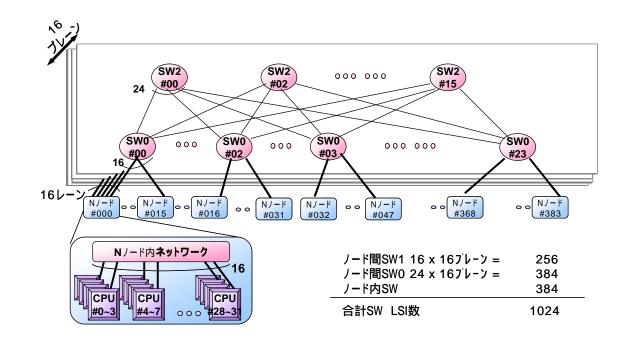

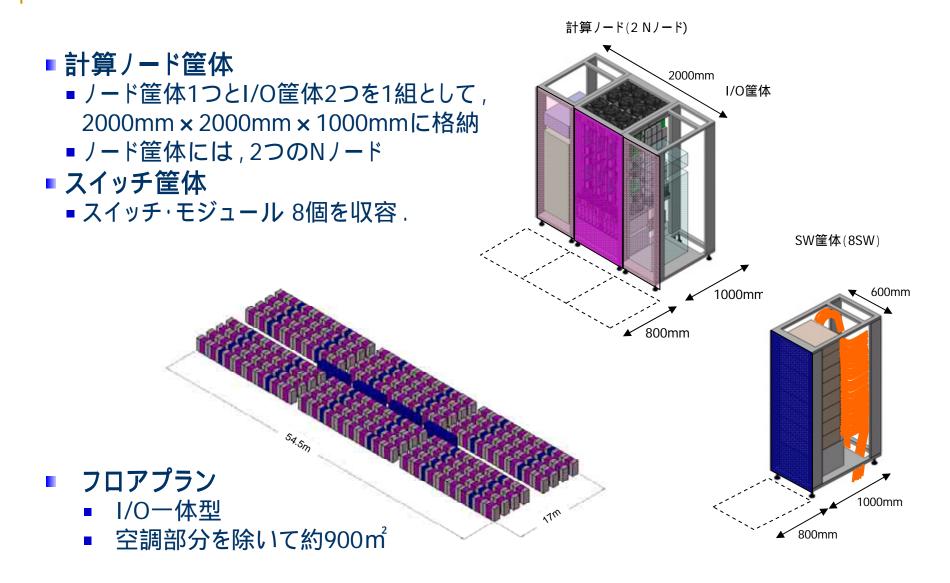

#### ユニットBの構成図

■ 計算ノード数: 12,288 (384 Nノード)

CPU数: 12,288コア数: 49,152

■ ピーク演算性能: 3.14PFLOPS

■ メモリ総容量: 0.375-0.75PB(計算ノード当り32-64GB)

■ Nノード: 32CPUs, NUMAノード, 1TB-2TB共有メモリ

■ 2段Fat-treeネットワーク: (24 + 16) x 16プレーン

■ 消費電力: 約7MW(周辺機器を含む)

■ 設置面積: 約900㎡(周辺機器を含む)

#### ユニットBの特徴

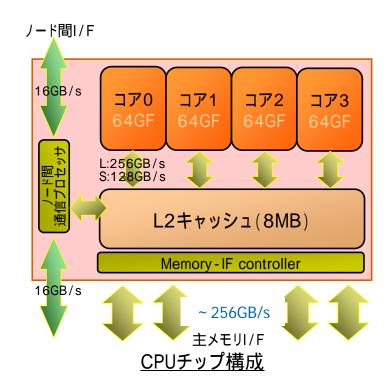

#### ■ プロセッサ

- 45nmプロセスによる1CPUチップ当り256GFLOPSの高性能演算器を実装

- 1CPU当り4コア構成,動作周波数2GHzで駆動

- コア当り8FMAx2セットの演算器と128KBの大容量ベクトルレジスタ

- 8MBのL2キャッシュを4コアで共有しソフトウェアでも制御可能としたRDB (Reusable Data Buffering)機能

- 全システムを12,288CPUで構成し演算性能3.14PFLOPS,主記憶0.375-0.75PBを実現

- システム運用のために、Nノード内の32CPUが論理的にメモリ空間を共有し、 一つのOSで動作

- 消費電力: 140W/CPU (Linpack実行時)

#### ネットワーク

- バイセクションバンド幅98TB/s, 2段のFat treeで384 Nノードを接続

- 光インターコネクトの採用

- 非同期転送,同報機能,高速バリア同期機能付きのデータ転送機能

- 入出力ポートの構成制御によるパーティショニング

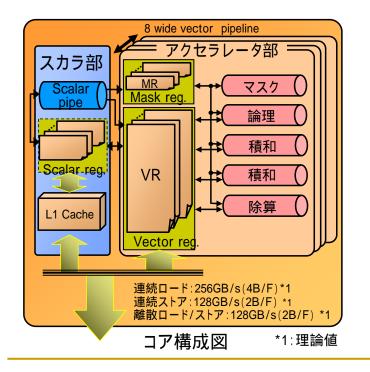

# プロセッサ構成

- 4コアを1チップ化

- 8MBのL2キャッシュ,メモリコントローラ,通信プロセッサから構成させる.

- 動作周波数2GHz

- コア当り64GFLOPS, CPU当り 256GFLOPS

- メモリバンド幅を, 1B/FLOP相当に増 強(詳細設計で検討)

- キャッシュ

- 8MBの共有L2キャッシュ

- 各コアとのバンド幅は,ロード256GB/s, ストア128GB/s

- 主メモリ間バンド幅は1B/FLOP相当

- データ供給能力は,L2キャッシュから各 コアのベクトルレジスタまで4B/FLOP

- RDB (Reusable Data Buffering)機能と呼ぶ選択的データ・キャッシング機能

|          | 仕様                                                                                  |

|----------|-------------------------------------------------------------------------------------|

| ピーク演算性能  | 256GF(64GFx4コア)<br>(ベクトルアクセラレータのみ)                                                  |

| L2キャッシュ  | 8MB(8way-セットアソシアティブ),<br>64B/ライン,4コア共有のUnifiedキャッ<br>シュ,選択的データキャッシング機能<br>(RDB機能)あり |

| メモリバンド幅  | 1B/FLOP相当                                                                           |

| ノード間バンド幅 | 16GB/s × 2                                                                          |

#### コア構成

- スカラ部

- 128本の汎用レジスタ

- 投機実行

- 4wayスーパースカラ

- ベクトル・アクセラレータ部

- 8セットの多重ベクトルパイプライン型アクセラレータ方式

- 積和演算器×2個

- 論理演算器,除算演算器,マスク演算器, ロード/ストア・パイプライン 各1個

|                      |         | 仕様                                                  |

|----------------------|---------|-----------------------------------------------------|

| ピ                    | ーク演算性能  | ベクトル: 64GF , スカラ: 4GF                               |

| 動                    | 作周波数    | 2GHz(ベクトル / スカラ)                                    |

| ベクトルアクセラレータ部(8VPP構成) |         |                                                     |

|                      | 演算器構成   | 積和x16 , 論理x8 , 除算x8 , マスクx8 , ロード/<br>ストアx8         |

|                      | レジスタ    | VR:64本以上(8Bx256要素/本)<br>MR:8本(256bit/本)             |

| ス                    | カラ部     |                                                     |

|                      | 演算器構成   | 乗算x1,加算x1,除算x1,整数x2                                 |

| レジスタ 128本(8B/本)      |         | 128本(8B/本)                                          |

|                      | L1キャッシュ | 命令:64KB(2wayセットアソシアティブ)<br>データ:64KB(2wayセットアソシアティブ) |

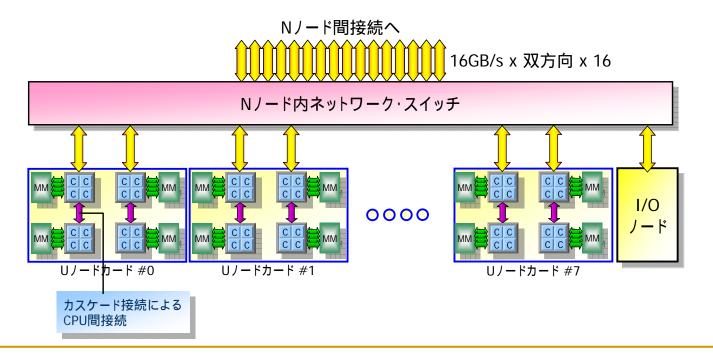

## Nノード構成

- 4個のCPUを1カードに搭載するUノードカード

- 8個のUノードカード(32CPU)と1つのI/Oノードをネットワーク・スイッチで接続したNUMAノード

- 2CPUが, Nノード用ネットワーク・スイッチ(33x33)にカスケード接続. 通信バンド幅は, 16GB/s x 2(双方向)

- 1つのI/Oノード(x86ベース)

- Nノード内入出力処理, Nノード内計算ノード管理など

#### Nノード間ネットワーク

- 2段のFat-treeネットワーク構成

- ポート当り16GB/s(双方向)の32×32スイッチ

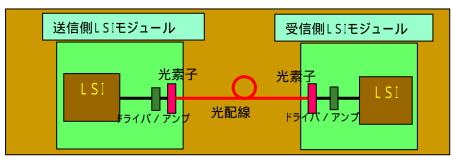

- スイッチ間の接続に,20Gbpsの光インターコネクトを採用

- 各Nノードから出る16レーンの接続をレーン毎にプレーン構成とし,システム 全体で16プレーン構成

- 384 Nノードを接続 . バイセクション・バンド幅98TB/sとなる

#### ■ 特徴

- 光インターコネクトの採用

- 非同期転送

- 同報機能

- 高速バリア同期機能 付きのデータ転送機能

- 入出力ポートの構成制 御によるパーティショニ ング

## 筐体実装及びフロアプラン

#### システム・ソフトウェアなど

#### ソフトウェア

- OS: Linux(フロントエンドノード, IOノード), 専用OS(計算ノード)

- ミドルウェア: 運用管理,ジョブ管理,SW配布,資源管理,グリッドミドルウェア(フロントエンド)

- ライブラリ: OpenMP, MPI, 科学技術計算ライブラリ

- ツール: 開発ツール, デバッグツール, チューニングツール

- プログラム言語コンパイラ

- Fortran , HPF , CAF , C/C++ , UPC

- プログラミングモデル

- 推奨モデル:分散メモリ並列,共有メモリ並列

60

#### RAS機能

- CPU

- ハードウェア診断回路

- ECCチェック: 大規模RAM(L2キャッシュ), チップ間I/F

- パリティチェック: その他RAM, 各データ バス

- 一部ユニット二重化チェック

- MOD-Nチェック, Out-of-Nチェック回路

- 制御回路のシーケンスチェック,タイミングチェック,タイムアウトチェック

- BIST (Built-In Test)回路

- 診断プログラム

- 自動診断プログラムによるパトロール チェック機能

- モニタ回路

- 温度, ノイズモニタ回路による異常状態検出/モニタリング機能

- メモリ

- LSIに関しては上記と同等

- ECCによる1ブロック(8b)エラー訂正,2ブロックエラー検出

- チップ故障救済機能

- Nノード間ネットワーク

- エラー検出/訂正

- パリティチェック, コードチェック, シーケンスチェック, データ長チェック

- 診断プロセッサによるOSストール監視, CPUなどの温度異常検出

- リトライ / 縮退運転

- Nノード自動再立ち上げ、I/Oリトライ

- Nノード縮退, Nノード間スイッチのプレーン縮退

- ストレージ・ファイルシステム

- ディスクアレイRAID6

- パス / I/O / ード冗長化

- 運用ソフトウェア

- 計算ノード、ファイルシステム、フロントエンドの的確な連携とシステム全体の信頼性の 確保

# 4. 要素技術について

#### 主な要素技術

- ユニットA

- SIMD型スカラプロセッサ技術(設計技術を含む)

- 低電力高性能チップ開発技術

- ToFuインターコネクト構成技術

- 部品単位水冷技術

- SIMD化コンパイラ技術

- 超並列用システムソフトウェア技術(データ管理含む)

- RAS技術

- ユニットB

- ベクトル・アクセラレータ型プロセッサ技術(設計技術を含む)

- 低電力高性能チップ開発技術

- Fat-treeネットワーク構成技術

- VCSELによる光インターコネクション技術

- 20Gbps SerDes技術, 局所水冷技術

- キャッシュ対応ベクトル化コンパイラ

- 超並列システムソフトウェア技術(データ管理含む)

- RAS技術

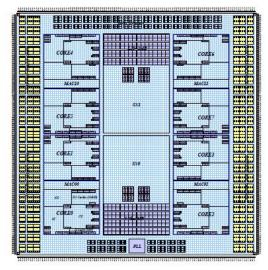

# 【ユニットA】 論理LSIの開発要素技術 (1/2) 論理LSIフロアプラン

#### ■ 高性能技術

- 富士通45nm半導体プロセス技術

- マルチコアLSI技術(8コア)

- HPC向け機能拡張コア

- コア当たり4つの浮動小数点積和演算器

- SIMD機構

- 共有2次キャッシュ(6MB)

- 高速バリア機構

- → 高いピーク性能(128GFLOPS)に加え,実 環境でも高い性能を発揮

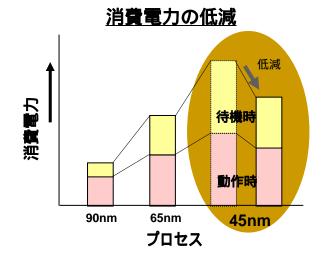

#### 低消費電力技術

- アクティブ電力,リーク電力削減技術

- 低温動作

- → 消費電力/性能を当社従来比10分の1

- → 小型 ~ 大型/ブレードサーバへ適用可能

|                      | 主な狙い       | ( :該当)      |

|----------------------|------------|-------------|

| 低消費電力技術              | アクティブ電 力削減 | リーク電<br>力削減 |

| クロック制御               |            | -           |

| RAMの電力削減             |            | -           |

| 省電力ラッチの採用            |            |             |

| Vth最適化               | -          |             |

| トランジスタサイズ最適化         |            |             |

| キャパシタセルのゲート<br>リーク削減 | -          |             |

| チップごとのVdd, Vbs制御     |            |             |

# 【ユニットA】論理LSIの開発要素技術 (2/2)

#### 高信頼性回路技術

- 高信頼技術

- メインフレーム用高信頼性回路技術

- ハードによるエラー検出&自己回復

- 低温動作

- 故障率の低減

- → ペタスケール (およそ10万個のプロセサ相当)のシステム運用を実現

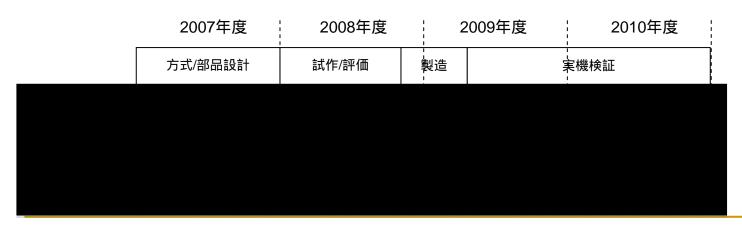

- 論理LSI開発スケジュール

|        |              | 種別                                                     | エラー検出方法              |  |

|--------|--------------|--------------------------------------------------------|----------------------|--|

|        | L1命令\$       | データ部                                                   | パリティビット              |  |

|        |              | タグ部                                                    | パリティビット              |  |

| L      | L1データ        | データ部                                                   | SEC · DED ECC        |  |

| 内蔵     | \$           | タグ部                                                    | パリティビット              |  |

| R<br>A | L2\$         | データ部                                                   | SEC · DED ECC        |  |

| M      |              | タグ部                                                    | SEC · DED ECC        |  |

|        | 命令・データ       | ラ mTLB                                                 | パリティビット              |  |

|        | ブランチ<br>ヒストリ | タグ部,データ部                                               | パリティビット              |  |

| 実      | レジスタ         | GPR , FPR , GUB , FUB ,<br>PC , PSTATE , 演算入出力<br>ラッチ等 | パリティビット              |  |

| 行部     | 演算器          | ALU,SHIFT,除算器,グラ<br>フィック演算器,比較器                        | パリティ予測回路             |  |

|        |              | 乗算器,FMA                                                | 剰余チェック回路<br>パリティ予測回路 |  |

|         |            |      |    |                | _ |

|---------|------------|------|----|----------------|---|

| 2007年度  | 2008年度     | 2009 | 年度 | 2010年度         |   |

| 基本·詳細設計 | 論理シミュレーション | 製造   |    | <br>  実機検証<br> |   |

|         |            |      |    |                |   |

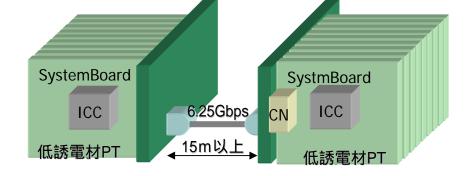

# 【ユニットA】インターコネクトの開発要素技術 (1/2)

#### ■ シリアルI/Oマクロ技術

- 6.25Gbps高速シリアル伝送

- プリエンファシス,イコライゼーション技術の確立

- 小面積,低消費電力を実現

→ 主流となりつつある,高速シリアル伝送技術を発展 汎用シリアルバス方式の高速化に寄与

#### 3.125Gbpsシリアルマクロ

#### ■ 高速信号伝送技術

- 6.25Gbpsデータ伝送技術の開発

- 低損失コネクタの開発

- 低誘電材料を使用したPT板開発

- ラック間15m以上のデータ伝送を実現

→ 高速伝送が必要とされるIDCでの汎用サーバ,ブレードサーバへの応用

# 【ユニットA】インターコネクトの開発要素技術 (2/2)

- ToFuインターコネクト

- 高帯域,低遅延伝送プロトコル

- 耐故障性にすぐれたシステム運用機構

- 集合通信処理を高速化するMPI処理オフロード機構

- 大規模メモリシステムを実現する分散メモリ機構

- 論理ピーク性能100PetaFlopsを超えるスケーラビリティ

- → ペタスケールコンピューティングに最適なインターコネクトの実現

- HPCだけでな〈汎用サーバへの転用も可能

- インターコネクト開発スケジュール

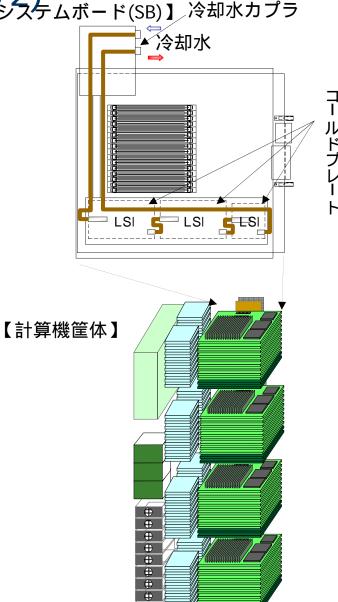

#### 【ユニットA】部品単位水冷技術(1/2) 「カード(SB)」 冷却水カプラ

#### ■ 高密度水冷機構

- 小型コールドプレート,小型冷却水 カプラを開発し,従来の水冷機構にはない 高密度実装を実現

- 空冷用ダクト空間削減による実装高密度 化

#### ■ ボード活性交換との両立

■ 故障したシステムボード(SB)の交換を,他 SBの稼働を継続したまま行える 冷水制御,漏水防止機構の開発

# 【ユニットA】部品単位水冷技術 (2/2)

- 半導体の稼動温度を下げて故障率を大幅に低減

- 空冷装置と比較してCPUの固定故障率を約0.006倍へ低減(理論計算値)

- 半導体の稼動温度を下げてリーク電流を低減

- 水冷による高効率な冷却の実現

- 効率良〈熱を部屋外へ移動できるため、データセンターで生じている廃熱問題を解決

- 冷却の高効率化は,計算機本体だけでな〈空調設備の省電力化,静音化,省スペース 化も実現

- 小型 ~ 大型/ブレードサーバへの展開

- 省電力化,静音化,高密度実装へ寄与

- 部品単位水冷開発スケジュール

# 【ユニットA】SIMD化コンパイラの開発要素技術 (1/2)

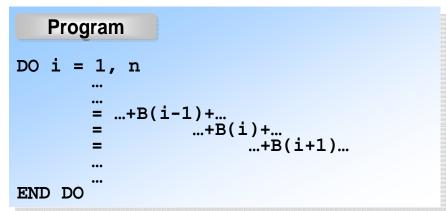

- SIMD機構の活用: コンパイラの命令スケジューリング機能を応用

- 並列化オーバヘッドのない細粒度の並列実行

- Basic, Extendの両ユニットで2並列実行

- 2演算/1命令

- Basic, Extendを独立使用し,条件実行時も両ユニットを並行動作

- SIMD機能の2演算を独立に使用し、 条件付演算もSIMD機構を 活用して並列実行

```

DO I=1,N

IF (条件(I)) then

A(I)=B(I)+C(I)

ELSE

X(I)=Y(I)*Z(I)

ENDIF

ENDDO

```

- プリフェッチによる メモリアクセス高速化

- L2, L1の両キャッシュ向けに 目的に応じてプリフェッチ命令を配置

```

DO I=1,N,2

IF (条件(I)) then

IF (条件(I+1)) then

A(I)=B(I)+C(I) A(I+1)=B(I+1)+C(I+1)

SIMD演算

ELSE

A(I)=B(I)+C(I) X(I+1)=Y(I+1)*Z(I+1)

EXTEND 側で計算

BASIC側で計算

ENDIF

ELSE

IF (条件(I+1)) then

X(I)=Y(I)*Z(I)

A(I+1)=B(I+1)+C(I+1)

BASIC側で計算

EXTEND側で計算

ELSE

X(I)=Y(I)*Z(I) X(I+1)=Y(I+1)*Z(I+1)

SIMD演算

ENDIF

ENDIF

ENDDO

```

# 【ユニットA】SIMD化コンパイラの開発要素技術(2/2)

- 自動並列化機能: Venusの8コアを1つの高性能コアのように活用

- 最内ループの並列化

- コア間共有キャッシュ,コア間高速同期機構の活用 粒度の小さい最内ループも自動並列化

- ベクトルより広範囲の適用可能性を追求

- マルチスレッドの特徴

- 制御オーバヘッドを縮小し,回転数の少ないループでも高速化が可能 回転数(ベクトル長)の確保が必須なベクトルに対する優位性

- SIMD化コンパイラ開発スケジュール

| 2007年度 | 2008年度 20    | 09年度 2010年     | F度<br>¦ |

|--------|--------------|----------------|---------|

| 詳細設計   | プログラミング/ 機能ホ | 実機検証 実機検証 /チュー | 証<br>ング |

|        |              |                | 1       |

|        |              |                |         |

|        |              |                |         |

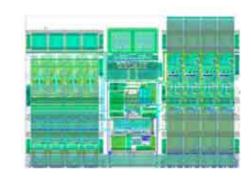

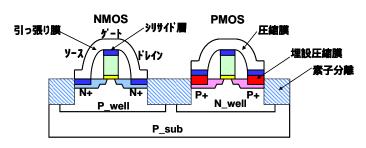

## 【ユニットB】論理LSI技術(1/2)

### (1) 要素技術の内容

・最先端半導体プロセストランジスタ構造

#### <u>論理LSI概要</u>

| プロセス     | 45nm CMOS,13層Cu配線 |

|----------|-------------------|

| 消費電力     | 最大140W            |

| 総トランジスタ数 | 最大7億              |

| 実装方式     | フリップチップ,ベアチップ実装   |

| クロックサイクル | 2GHz              |

- ·LSI回路技術

- √高速·高集積LSIを実現する回路技術

- ✓動作時/待機時両方の消費電力低減技術

- ·LSI設計技術

- √高い設計品質の確保を目指した検証技術

- ✓高速・高集積を実現するレイアウト設計技術

### (2) 革新性,発展性,技術力強化への寄与

- ·最先端·高性能45nmCMOSプロセスの採用(歪みシリコン, Low etcの先進技術適用)

- ・高速・高集積回路技術確立(高速内部セル/SRAM , 高速インタフェース , 高速クロック分配etc)

- ・高速性と両立する低消費電力回路技術の確立(マルチVth,クロックゲーティングetc)

- ・上記確立した技術を,他の製品領域(高性能サーバー,デジタル家電etc)に展開

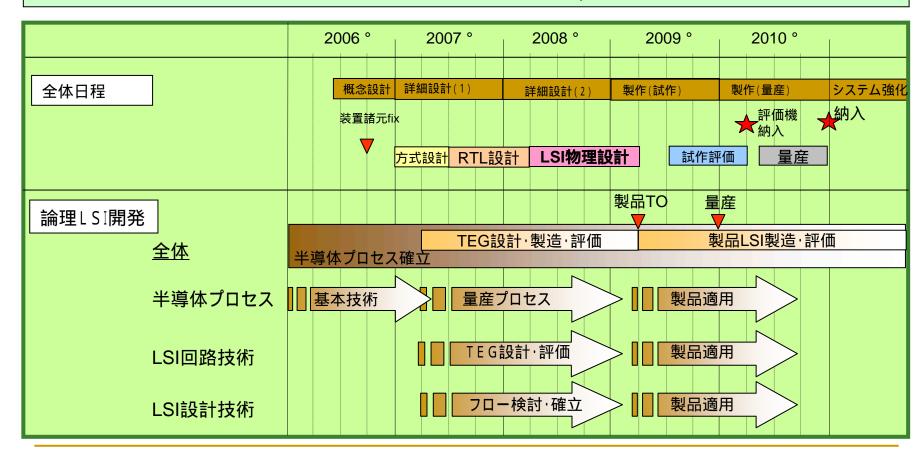

# 【ユニットB】論理LSI技術(2/2)

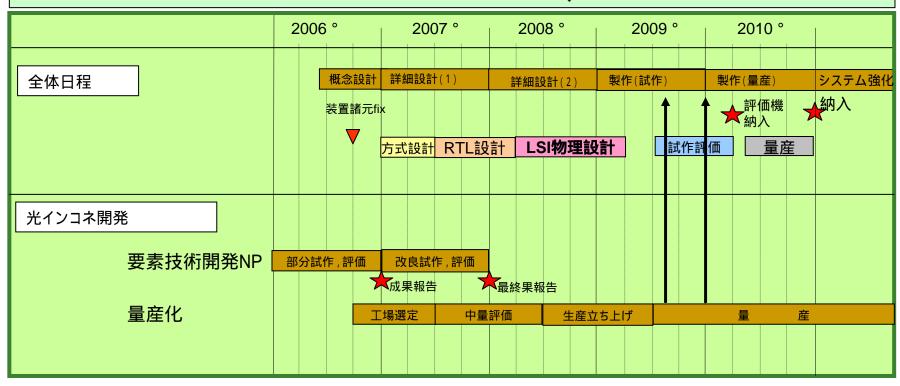

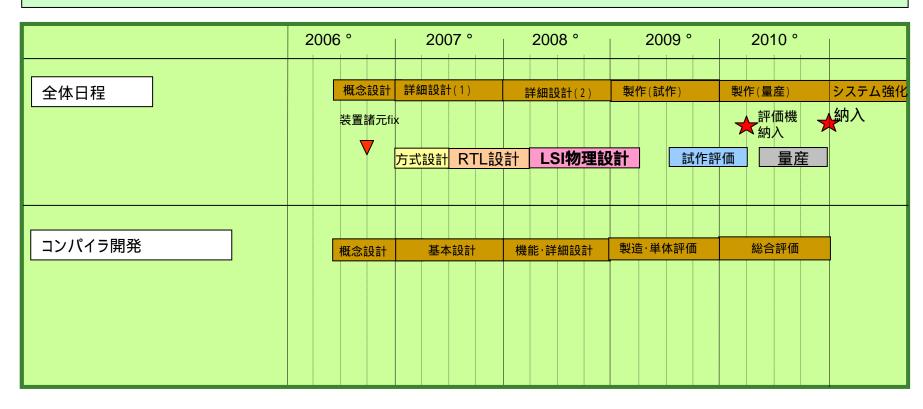

論理LSI開発日程

TEG設計開始 ; 2007年度/1Q末

製品LSI テープアウト ; 2009年度/1Q末

LSI製造量産開始 ; 2009年度/4Q末

## 【ユニットB】光インターコネクト技術(1/2)

### (1) 技術開発内容

LSI間の信号伝送を従来の電気伝送に変わって光で伝送,部分水冷技術

### 具体的な研究項目

·高速光素子に関する開発 発光素子, 受光素子 ·高密度実装に関する開発 高速光電気実装技術,高密度光配線技術,冷却モジュール技術,他

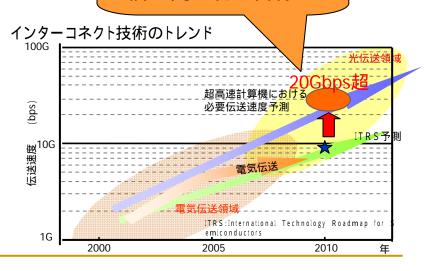

(2)革新性,発展性,技術力強化への寄与

#### 開発目標

·高速化: 20Gbps超SerDes技術 ITRS予測の2倍 電気伝送の限界5~10Gbpsを打破

·小型化:1000信号/LSI 従来の1/200

·消費電力:従来比1/100

・高信頼度,低コスト化

## 次世代スパコン実現に寄与

さらに

·ハイエンドサーバ,ファイルサーバネット ワーク機器

- ·PC,携帯端末,情報家電

- ・医療機器,車 ・・・・・ への活用が期待される

光技術よりITRS予測の 2倍の高速化を目標

## 【ユニットB】 光インターコネクト(2/2)

光インターコネクト開発日程

要素技術開発完了 : 2007年度/4Q末

インタフェース仕様FIX : 2007年度/4Q末

量産工場選定 : 2007年度/2Q末

中量評価完了 : 2008年度/2Q末

生産立ち上げ : 2009年度/20末

量産開始 : 2009年度/3Q~

## 【ユニットB】 キャッシュ対応ベクトル化コンパイラ(1/2)

## (1) 技術開発内容

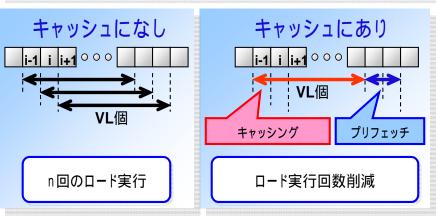

データをキャッシュに登録するかしないかをソフトウェア(コンパイラ)から制御する 技術で,再利用性の高いデータを選んでキャッシュに登録することにより,キャッシュ

容量の有効利用を図る.

#### 具体的な技術項目

- ・自動的に適用配列を選択する技術

- ・自動的に非適用配列を選択する技術

- ・指示行で適用配列を指定する技術

- ・指示行で非適用配列を指定する技術

## (2)革新性,発展性

キャッシュ対応技術により、メモリバンド幅維持と短レイテンシ化を実現.

- ・登録データの選択によるキャッシュの有効利用

- メモリレイテンシ隠蔽

- キャッシュ格納済み配列のロードバンド幅高

- バンク競合率低減

- 短ベクトル長時の実行性能向上

- ・SWプリフェッチ機能によるメモリレイテンシ隠蔽

# 【ユニットB】キャッシュ対応ベクトル化コンパイラ(2/2)

コンパイラ開発日程

基本設計完了 : 2007年度/4Q末

機能·詳細設計完了 : 2008年度/4Q末

製造·単体評価完了 : 2009年度/4Q末

総合評価完了 : 2010年度/4Q末

# 5. ベンチマーク・テスト性能評価について

## ベンチマーク・テストによる性能評価について

- ベンチマーク・テスト・プログラム(21本)の実行時間を推定

- 特に,ベンチマーク・テスト・プログラム(9本)について,詳細に評価

- ターゲット・アプリケーションから7本のベンチマーク・テスト

- SimFold , GAMESS , Modylas , RSDFT , NICAM , LatticeQCD , LANS

- HPL(High Performance Linpack), NPB-FT

- 推定方法は,両者独自の手法を採用

- 実機での計測値から推定

- 新たなアーキテクチャ部分は,机上で分析,評価

# NH案の評価手法概要(1/4)

# NH案の評価手法概要(2/4)

# NH案の評価手法概要(3/4)

# NH案の評価手法概要(4/4)

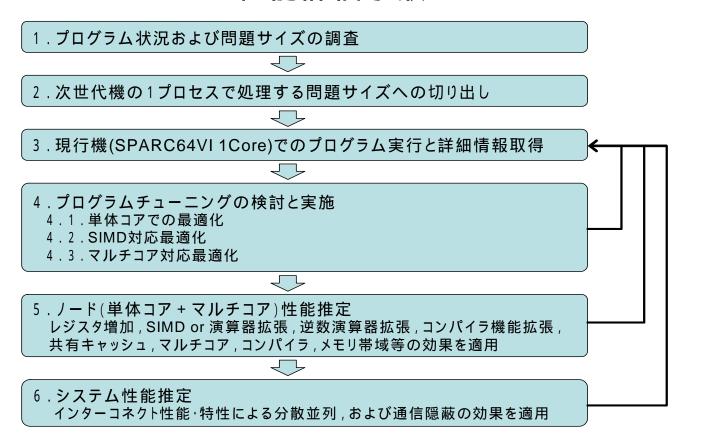

## F案の評価手法概要(1/2)

- 演算部分と通信部分に分けて実機での計測値から推定、新たなアーキテクチャ部分は, 机上で分析, 評価

- 演算部分の推定方法

## 性能評価手順

# F案の評価手法概要(2/2)